FPGA(现场可编程门阵列)技术作为现代电子系统设计的核心,以其高度的灵活性和并行处理能力,在通信、图像处理、人工智能等领域发挥着日益重要的作用。其传统的设计方法往往涉及复杂的硬件描述语言(如Verilog或VHDL)和繁琐的设计流程,对初学者乃至经验丰富的工程师都构成了一定的门槛。明德扬至简设计法应运而生,旨在化繁为简,提供一套高效、清晰、易于掌握的FPGA设计与开发方法论。本教程总汇将系统性地阐述该设计法的核心理念、实践步骤,并关联其在计算机软硬件协同开发中的关键角色。

一、 明德扬至简设计法的核心理念

“至简”并非意味着功能简化,而是追求设计思路与流程的极致清晰与高效。其核心在于:

- 模块化与层次化:将复杂系统分解为功能明确、接口清晰的独立模块。每个模块专注于单一功能,通过标准化的接口进行互联,极大降低了系统整体的设计和调试复杂度。

- 模板化与模式化:针对FPGA设计中常见的功能单元(如状态机、FIFO、数据流处理单元等),出经过验证的、最优化的设计模板。开发者只需根据具体参数进行适配,避免了重复劳动和潜在错误。

- 可视化与流程化:强调设计过程的可视化管理,通过清晰的流程图、时序图来规划逻辑。设计流程被固化为明确的步骤(需求分析->模块划分->接口定义->代码实现->功能仿真->综合实现->板级调试),使开发过程井然有序。

- 软硬件协同思维:在设计初期就综合考虑硬件(FPGA逻辑资源、时序、功耗)与软件(驱动、应用程序、算法)的划分与交互,追求整体系统的最佳性能与成本平衡。

二、 FPGA精简设计流程详解(基于至简法)

- 需求分析与规格定义:明确系统需要完成的任务、性能指标(如处理速度、数据带宽、延迟)以及外部接口。这是所有设计的基石。

- 系统架构与模块划分:根据需求,绘制系统框图。将总功能划分为数个协同工作的子模块,例如:数据采集模块、算法处理核心、存储控制模块、通信接口模块等。明确定义每个模块的输入、输出信号及时序关系。

- 接口标准化与协议制定:模块间采用简单、统一的接口协议(如简单的握手信号、标准总线协议AXI-Stream等),这是保证模块能够像“积木”一样灵活组合的关键。

- 模板化代码实现:使用Verilog或VHDL,但代码结构严格遵循预设模板。例如,状态机采用“三段式”写法,确保代码清晰且综合结果可靠。重点描述模块的“行为”而非过于底层的电路结构。

- 高效仿真验证:搭建分模块和系统级的测试平台(Testbench),进行充分的仿真测试。至简法鼓励使用自动化脚本和断言(Assertion)来提高验证效率。确保逻辑功能在进入硬件前已基本正确。

- 综合与实现约束:利用FPGA厂商工具进行综合、布局布线。此阶段需合理添加时序、引脚、区域等约束,以确保设计能在目标芯片上稳定运行于指定频率。至简法强调约束文件的规范化和可重用性。

- 板级调试与验证:将生成的比特流文件下载到FPGA开发板,结合逻辑分析仪(如ILA)、芯片自带的调试内核进行实时信号抓取和分析,快速定位并解决问题。

三、 与计算机软硬件技术开发的深度融合

FPGA从来不是孤立存在的,它通常是更大计算系统的一部分。至简设计法尤其注重这种协同:

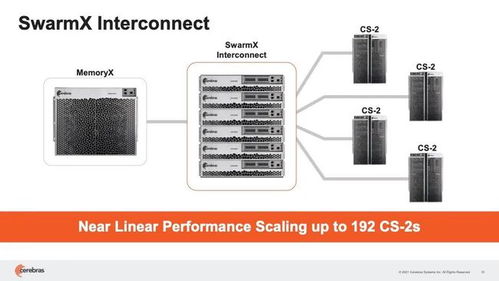

- 作为硬件加速器:在异构计算体系中,FPGA常作为CPU的协处理器,用于加速特定的计算密集型任务(如加解密、视频编解码、神经网络推理)。至简法指导如何设计高效、接口标准的加速器IP,以便通过PCIe等总线与主机CPU顺畅通信。

- 软硬件接口设计:设计精简而完备的寄存器配置接口(通常通过APB、AXI-Lite等总线),使得上层软件(驱动程序、应用程序)可以方便地控制FPGA功能、查询状态、传输数据。这是软硬件联调成功的前提。

- 系统级建模与验证:在前期,可以使用高级语言(如C/C++、SystemC)或基于FPGA的仿真环境,对包含软件算法和硬件逻辑的完整系统进行建模和性能评估,指导硬件/软件功能的合理划分。

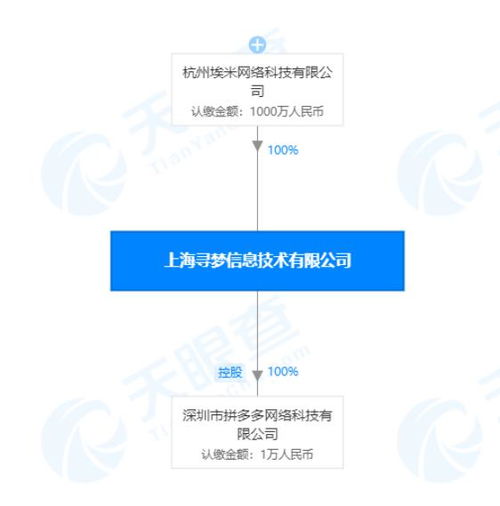

- 嵌入式SoPC开发:在集成硬核处理器(如ARM Cortex)的FPGA(如Zynq系列)上,至简法同样适用。它指导如何构建自定义的硬件外设(PL部分),并集成到处理器系统(PS部分)中,通过统一的软件开发环境(如Vitis)进行应用程序开发,实现真正的单芯片系统解决方案。

四、 与学习路径建议

明德扬至简设计法为FPGA学习者和开发者提供了一条从入门到精通的清晰路径。它通过将复杂问题模块化、将通用方法模板化、将开发流程标准化,显著降低了学习曲线,提升了设计质量和开发效率。

建议学习路径:

1. 基础入门:掌握数字电路基础、Verilog语法。

2. 方法学习:深入理解至简设计法的模块划分、模板代码和设计流程。

3. 工具熟悉:熟练使用一种主流FPGA开发工具(如Vivado、Quartus)及其仿真、调试功能。

4. 项目实践:从简单项目(如数码管显示、串口通信)开始,严格遵循至简流程进行实践。

5. 系统拓展:尝试涉及软硬件交互的项目,如基于MicroBlaze或Zynq的嵌入式系统设计,或参与包含算法加速的完整系统开发。

通过践行至简设计法,开发者不仅能高效完成FPGA逻辑设计,更能培养出色的系统架构思维,成为契合当今软硬件协同开发趋势的复合型技术人才。